Discover how to convert processor clock speed from MHz to seconds per cycle using this technical guide for accurate conversions.

This article explains conversion formulas, real-world examples, and technical details, empowering readers to master processor timing with ease swiftly precise.

AI-powered calculator for Converter from processor clock speed (MHz to seconds per cycle)

Example Prompts

- 125 MHz

- 250 MHz

- 500 MHz

- 1000 MHz

Understanding Processor Clock Speed and Cycle Time

Processor clock speed is a fundamental parameter in digital electronics that determines how fast a processor executes instructions. Measured in megahertz (MHz), it quantifies millions of cycles per second, setting the pace for all digital operations.

The conversion from MHz to seconds per cycle is essential for evaluating processor performance, ensuring synchronization in embedded systems, and accurately simulating hardware behavior. This guide details every step of the conversion process, clarifying formulas, variables, and practical applications.

Fundamental Concepts

In computer architecture, the clock cycle represents the basic time unit during which a processor completes one operation or a fraction of an instruction. The clock speed, given in MHz, translates to the number of these cycles per second. Understanding this relationship is pivotal for engineers designing systems that require precise timing.

Processor clock frequency and cycle time are inversely proportional. A higher clock frequency means a shorter cycle time, enabling the processor to perform more operations per second. Conversely, lower clock speeds result in longer cycle times, which can impact system responsiveness and overall performance.

Conversion Formulas and Variables

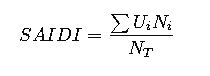

To convert processor clock speed from MHz to seconds per cycle, the primary formula is based on the inverse relationship between frequency and period. The period (T) represents the duration of one cycle and is given by:

In this formula:

- T is the cycle time, expressed in seconds per cycle.

- f is the processor clock speed in megahertz (MHz).

- The multiplication by 10⁶ converts megahertz to hertz (cycles per second) because 1 MHz = 1,000,000 Hz.

This simple formula is critical in electronics and computer engineering when comparing processors, setting up timing constraints, or designing systems that require synchronization.

When using the formula, ensure that the units are consistent so that the outcome is accurate. This conversion holds true irrespective of the processor’s architecture, making it universally applicable across various digital designs and embedded systems.

Extended Formulas and Considerations

In some scenarios, you might encounter additional parameters that modify the effective cycle time. Consider factors like pipeline stages or clock multipliers in advanced processors. While the basic conversion from MHz to seconds per cycle remains unchanged, other factors can affect the overall effective cycle time in practical applications.

For instance, if a processor uses a pipeline architecture, each cycle might not correspond directly to a single executed instruction. However, the foundational formula still aids in the raw conversion from clock speed to basic cycle length. Understanding these nuances can provide deeper insights into performance tuning and design optimizations.

Extensive Conversion Tables

Below are extensive tables designed to provide a quick reference for typical processor clock speeds and their corresponding cycle times. These tables are especially helpful for engineers and students who need rapid conversions during design or analysis phases.

| Clock Speed (MHz) | Cycle Time (seconds per cycle) |

|---|---|

| 1 | 1.0 × 10-6 |

| 50 | 2.0 × 10-8 |

| 100 | 1.0 × 10-8 |

| 250 | 4.0 × 10-9 |

| 500 | 2.0 × 10-9 |

| 1000 | 1.0 × 10-9 |

In addition to the basic conversion, engineers should be aware of tolerances and factors such as power consumption, thermal design, and potential clock drift. The above table offers a straightforward lookup for raw values and cycle times, which forms the backbone of timing analysis in many applications.

The table is designed for readability with alternating row colors and clear borders. Such visual presentation is essential when referencing data quickly during design reviews or technical discussions.

Practical Applications and Real-life Examples

Understanding how to convert processor clock speeds into cycle times is not merely academic; it has practical, real-world applications across various fields. Two predominant areas include embedded system design and performance analysis in modern microprocessors.

Below, we discuss two detailed examples to illustrate real-life applications of these concepts. Each example demonstrates the step-by-step process, enabling readers to grasp the calculation’s relevance and utility.

Example 1: Embedded System Timer Calibration

Consider an engineer developing an embedded system for an industrial application where precise timing is critical. The system uses a processor with a clock speed of 200 MHz. The engineer needs to calculate the cycle time to program a timer interrupt accurately.

Using the conversion formula: T = 1 / (f × 106), where f = 200 MHz, the calculation is as follows:

- Multiply the clock speed by 106: 200 × 106 = 200,000,000 cycles per second.

- Take the inverse: T = 1 / 200,000,000 seconds per cycle.

- This results in T = 5.0 × 10-9 seconds per cycle.

This calculation informs the engineer that each cycle occupies 5 nanoseconds. The precise cycle timing ensures that the programmed timer interrupt can accommodate all required calculations, thus guaranteeing reliable system performance even under critical operational conditions.

Moreover, this conversion allows for fine-tuning delays in software algorithms and ensures that hardware and software operations stay synchronized in real time. The cycle time value is pivotal in debugging and calibrating the microcontroller’s performance.

Example 2: Performance Analysis in CPU Simulations

Imagine a scenario where a systems engineer is tasked with evaluating a new processor design for high-performance computing. The design specifications indicate a clock speed of 1500 MHz. To simulate the processor’s behavior accurately, the engineer must determine the duration of one cycle.

By applying the formula T = 1 / (f × 106):

- Convert 1500 MHz to hertz: 1500 × 106 = 1,500,000,000 Hz.

- Calculate T = 1 / 1,500,000,000 seconds per cycle.

- The cycle time becomes approximately T = 6.67 × 10-10 seconds per cycle.

This short cycle time of approximately 0.667 nanoseconds per cycle reflects the processor’s capability for rapid execution of instructions. Such precise simulation data allow engineers to model the processor’s performance under high loads, optimize instruction-level parallelism, and identify potential bottlenecks in the architecture.

The conversion not only aids in the simulation process but also provides insight into how the design may perform in real-world deployments, enhancing both the design validation process and future optimization strategies.

Advanced Considerations in Clock Speed Conversion

While the conversion formula is straightforward, some advanced topics warrant consideration for engineers aiming for high precision. For instance, temperature variations, manufacturing tolerances, and power supply fluctuations can impact actual timing behavior in real-world silicon.

Advanced systems might employ calibration routines that adjust the effective clock speed based on operating conditions. In such cases, the base conversion is still critical, but additional correction factors may be applied. Understanding the underlying formula gives engineers a foundation upon which to build more complex timing models.

Impact of Pipeline Architectures

Modern processors often incorporate deep pipelines to increase instruction throughput. A pipeline splits the execution path into several stages where different parts of multiple instructions are processed concurrently. While the clock cycle remains as calculated, the effective instruction throughput is boosted due to parallelism.

For example, a processor with a high clock speed might have a five-stage pipeline. In such designs, the cycle time calculated from the clock frequency is used as a baseline. However, the total latency for a complete instruction is the product of the cycle time and the number of pipeline stages. This nuance is essential for performance engineers analyzing instruction execution and throughput.

Clock Multipliers and Dividers

Some microprocessors use additional clock multiplication or division techniques to achieve higher internal clock rates from a lower external frequency source. While the external clock speed is provided in MHz, the effective internal speed may be different due to these multipliers. Engineers must adjust calculations accordingly.

The basic conversion formula T = 1 / (f × 106) holds true for the provided input frequency. When clock multipliers are involved, it is vital to multiply the given frequency by the multiplier before applying the formula. For instance, if an external clock of 50 MHz is multiplied by a factor of 4, the effective frequency is 200 MHz and T must be calculated as 1 / (200 × 106).

Designing Reliable Timing Systems

Accurate conversion of processor clock speed to seconds per cycle is crucial in the design of reliable timing systems. Whether for industrial control, consumer electronics, or high-performance computing, the integrity of timing data underpins system performance and reliability.

Designers use the cycle time to program delays, synchronize data transfers, and coordinate multi-core operations. For example, when designing a digital communication system, engineers rely on precise cycle times to ensure that transmitted and received data are aligned correctly, thereby reducing errors and improving overall performance.

Synchronization in Distributed Systems

In distributed computing environments, clock synchronization is critical. Each node’s processor cycle time, determined through the conversion process, must be precisely aligned with the system’s master clock. Any deviation can lead to errors in data consistency, especially in systems like financial transaction processing or industrial automation.

Engineers deploy techniques such as Network Time Protocol (NTP) and Precision Time Protocol (PTP) where understanding the cycle time is essential for setting synchronization parameters. The accurate conversion from MHz to seconds per cycle is a fundamental step in calibrating these systems to maintain global time accuracy and ensure coordinated operations across nodes.

Low-power and Battery-operated Devices

For battery-operated devices and Internet of Things (IoT) applications, optimizing power consumption is paramount. Lower clock speeds can drastically reduce power usage but may also increase cycle time. Designers must balance performance with power efficiency by calculating the exact cycle time based on the chosen frequency.

An accurate conversion helps in determining the minimal operational parameters necessary to achieve a desired level of performance while minimizing energy usage. In low-power applications, even milliseconds of delay per cycle may accumulate to significant power savings, making this conversion an essential part of the design process.

Additional Conversion Tables for Specific Applications

For further clarity, here is an additional table that breaks down conversion examples into different operational scenarios, such as low-power applications versus high-performance computing environments. These tables illustrate how various clock speeds translate into cycle time under different design constraints.

The following table showcases a range of processor speeds frequently employed in both embedded systems and desktop processors, with cycle times presented in scientific notation for clarity and precision.

| Application Scenario | Typical Clock Speed (MHz) | Calculated Cycle Time (seconds per cycle) |

|---|---|---|

| Low-Power IoT Device | 16 | 6.25 × 10-8 |

| Mobile Processor | 1200 | 8.33 × 10-10 |

| Desktop CPU | 3200 | 3.125 × 10-10 |

| High-end Server | 4000 | 2.5 × 10-10 |

This table emphasizes the variability of design specifications. Engineers can consult these values during the initial phases of system design or when optimizing existing systems, thereby ensuring that every component operates within its intended timing constraints.

Combining these tables with robust formulas provides a comprehensive toolkit for engineers involved in both theoretical and practical aspects of processor design and system optimization.

FAQs on Converter from Processor Clock Speed (MHz to Seconds per Cycle)

Q1: What is the significance of converting MHz to seconds per cycle?

A: Converting MHz to seconds per cycle helps engineers determine the duration of each clock cycle, crucial for timing analysis, system synchronization, and performance tuning in digital circuits.

Q2: Can this formula be applied to any processor regardless of its architecture?

A: Yes, the formula T = 1 / (f × 106) applies universally as it is based on physical principles, although additional factors may be considered in advanced architectures.

Q3: How do pipeline architectures affect the calculation of cycle time?

A: While the fundamental cycle time remains as computed from the clock speed, pipelines can overlap instruction executions, altering effective throughput but not the basic cycle duration.

Q4: Should I use extra correction factors when converting MHz to seconds per cycle?

A: For basic conversions, no. However, in scenarios involving clock multipliers, dividers, or calibration adjustments, you must incorporate additional multipliers to account for those effects.

External Resources and Further Reading

For additional insights on processor timing and digital circuit design, the following authoritative resources are recommended:

- Intel Processor Architecture

- ARM Architecture Overview

- All About Circuits – Clock Frequencies Explained

- Electronics Notes – Oscillator and Timing Design

These links offer deeper technical details and case studies which further elucidate the importance of precise timing in digital systems.

Engineers, designers, and enthusiasts alike will find a wealth of information on these pages, enhancing their understanding of complex processor timing issues and real-world applications.

Best Practices in Engineering Conversions

Adopting rigorous best practices is vital when converting and using processor timing data. Here are some procedures to ensure robust conversion and system design:

- Always verify unit consistency—double-check that megahertz values are correctly converted to hertz before calculating cycle time.

- Use detailed design documentation that records clock speeds, correction factors, and environmental considerations.

- Simulate timing in software before implementing hardware changes; advanced simulation tools can help account for pipeline effects and clock multipliers.

- Cross-reference calculated values with datasheets and manufacturer guidelines to ensure design safety margins.

Integrating these best practices reinforces system reliability, minimizes design errors, and guarantees optimal performance under diverse operational conditions.

Reviewing these procedures regularly helps engineers remain updated with the evolving landscape of digital processor design and timing specifications.

Additional Real-world Case Study

Consider a scenario from the telecommunications industry where precise synchronization between multiple digital systems is a must. A network switch uses a custom processor operating at 800 MHz. Accurate conversion to seconds per cycle allows network engineers to design high-speed data transfer protocols and fine-tune error-correction algorithms.

Using the formula, the conversion is as follows:

- f = 800 MHz, so 800 × 106 = 800,000,000 cycles per second.

- Cycle time, T = 1 / 800,000,000 = 1.25 × 10-9 seconds per cycle.

This value is key to precisely delaying and aligning packet transmissions, minimizing jitter and enhancing overall network performance. The network switch can process data consistently, ensuring minimal latency during high-volume data transfers. Detailed timing analysis like this is critical for the telecommunications sector, where even nanosecond discrepancies can impact service quality and reliability.

Moreover, synchronization algorithms derived from these precise calculations help maintain clock alignment across distributed systems, which is essential for coordinated network operations in data centers and telecommunication infrastructures.

Integrating the Converter in Software Tools

Modern engineering software often includes modules for converting clock speeds to cycle times. Integrators can embed the conversion formula into applications such as system simulators, digital design verification tools, and embedded systems IDEs.

This integration automates the conversion process, reduces the chance of human error, and speeds up simulation times. For instance, a timing analysis module within a popular embedded system design tool can allow a designer to simply input the MHz rating, and the tool will instantly display the corresponding cycle time along with additional timing details like setup and hold times. Such automation is essential for rapid prototyping and iterative design cycles.

Comparative Analysis of Different Processor Designs

By utilizing the converter from MHz to seconds per cycle, engineers can compare various processor designs across different market segments. Whether evaluating low-power microcontrollers versus high-performance CPUs, the conversion offers a normalized metric to assess potential performance.

This normalized metric is beneficial during early design reviews. A design team may assess multiple architectures using a common timing threshold, ensuring that the chosen component meets the system’s performance and power criteria. Comparative tables can streamline this process, making it easier to identify the best candidates for any given application.

| Processor Type | Clock Speed (MHz) | Cycle Time (seconds per cycle) | Application |

|---|---|---|---|

| Microcontroller | 16 | 6.25 × 10-8 | Sensor Networks |

| Mobile CPU | 1200 | 8.33 × 10-10 | Smartphones |

| Desktop Processor | 3200 | 3.125 × 10-10 | Gaming PCs |

| Server CPU | 4000 | 2.5 × 10-10 | Data Centers |

This comprehensive comparative analysis underscores the benefits of accurate timing conversions when evaluating diverse processor platforms. Such systematic comparisons are invaluable during the component selection process for any high-reliability design.

As this article demonstrates, understanding processor timing through the conversion of MHz to seconds per cycle is a critical tool in the engineer’s arsenal, facilitating effective decision-making and robust system design.

Final Thoughts on Converter from Processor Clock Speed

Accurate timing is the backbone of modern digital systems, and understanding the conversion from processor clock speed (MHz) to seconds per cycle stands as a critical skill for engineers. Whether in embedded systems, high-performance computing, or network communication infrastructures, precision is paramount.

Engineers are encouraged to leverage the provided formulas, explanatory tables, and real-world examples as they design, analyze, and optimize digital architectures. By grasping these fundamental concepts, practitioners can ensure that their systems operate predictably and efficiently under various conditions.

Additional FAQs and Engineering Insights

Q5: How do environmental factors affect the reliability of the cycle time conversion?

A: Environmental conditions (e.g., temperature, voltage fluctuations) can cause minor deviations in clock performance. However, the basic conversion remains accurate, and designers account for these factors through calibration and tolerance margins.

Q6: Where is this conversion most widely used?

A: This conversion is ubiquitous across digital electronics design, from microcontrollers in IoT devices to high-end CPUs in data centers, where precise timing is critical.

Q7: How can simulation tools help in reinforcing the theoretical conversion?

A: Simulation tools incorporate the conversion formula within their timing analysis modules, allowing engineers to model real-world performance and optimize designs before hardware implementation.

Q8: Can I apply these conversions to analogue circuits?

A: While the conversion formula is specific to digital processors, the concept of period and frequency is also relevant in analogue circuits, though additional factors may come into play.

These FAQs address common concerns and enhance the understanding of when and how to use the MHz-to-seconds per cycle conversion effectively.

Staying current with engineering best practices and using accurate conversion methods is essential for maintaining cutting-edge designs in today’s fast-paced digital world.

Conclusion

By mastering the conversion from processor clock speed in MHz to seconds per cycle, engineers gain a powerful tool for designing, analyzing, and optimizing digital systems. The clarity offered by our comprehensive guide, complete with formulas, tables, and real-world examples, empowers professionals to create timing-critical designs with confidence.

This article serves as an authoritative reference that bridges theoretical concepts and practical applications. Whether you’re a seasoned engineer or a student seeking in-depth understanding, employing these conversion techniques will undoubtedly enhance your design processes, ensuring precision and reliability in your projects.